《逻辑与计算机设计基础(原书第5版)》——2.8 硬件描述语言简介

本文共 3084 字,大约阅读时间需要 10 分钟。

2.8 硬件描述语言简介

设计复杂系统和集成电路没有计算机辅助设计(CAD)工具的帮助是不行的。原理图输入工具(schematic capture)支持绘制模块和所有层次的互连。在原语与功能模块级,CAD工具提供了图形符号库(library)。原理图输入工具通过生成层次模块符号和复用这些符号来构建层次结构。

库中的原语块和功能模块符号联合建模,允许对各个层次块的行为和时序,以及整个电路进行验证。这种验证是为模块或电路提供输入,利用一个逻辑模拟器(logic simulator)确定输出。库中的原语块还有一些相关的数据,例如物理面积和延迟参数,逻辑综合器(logic synthesizer)可用这些数据优化由硬件描述语言描述的、自动生成的设计。正如2.1节简要描述的那样,尽管图形和布尔等式对小电路来说是够用的,但硬件描述语言在开发大型复杂电路的现代化设计过程中已经变得至关重要。硬件描述语言类似于程序设计语言,但是它们有一些特别的属性,适合描述硬件的结构与行为。它们明显地不同于典型的程序设计语言,因为它们可以描述由硬件完成的并行操作,而大多数程序设计语言描述串行操作。正如我们将在本章的剩余部分和第3章与第4章中介绍的那样,硬件描述语言的威力是在它被用来不仅仅表示结构信息时变得更为明显。它能表示布尔等式、真值表以及一些如算术运算那样的复杂操作。因此,在自顶向下的设计方法中,整个系统的高层描述可以用硬件描述语言精确地确定。作为设计过程的一部分,这个高层描述又可以修改,划分成较低层的描述。最后,得到用原始组件和功能模块表示的最终描述,并作为设计过程的结果。要注意的是所有这些描述都可以仿真。因为它们表示相同功能的系统,只是定时不同,对相同的输入它们都会产生相同的响应,给出一样的逻辑值。这个重要的仿真特性支持设计验证,是硬件描述语言被应用的主要原因之一。硬件描述语言被不断广泛使用的最主要原因是逻辑综合。系统的硬件语言描述可以用一个中间级(称为寄存器传输语言(RTL)级)来表示。逻辑综合工具与附带的组件库可以将这样的描述转换成原语组件之间的相互连接来实现电路。这种代替手工的逻辑设计方法大大提高了复杂逻辑设计的效率。逻辑综合器将用硬件描述语言描述的电路的寄存器传输语言级描述转换成一个优化了的网表,网表表示存储元件和组合逻辑。所包含的优化远比本章以前所介绍的要复杂,但它们有许多相同的概念。逻辑优化完成之后,网表可以用物理设计工具将其转换成实际的集成电路版图或现场可编程门阵列(FPGA)。逻辑综合工具负责设计大部分细节,并允许设计者在各种设计约束之间取得折中,这对于先进的设计来说是必需的。VHDL和Verilog是当前广泛使用的标准硬件设计语言。这两种语言的标准由电气与电子工程师协会(IEEE)制定、完善、发行。这些语言的所有实现都必须遵循各自的标准。这种标准化使硬件描述语言相对于原理图法具有另一个优势,即这种标准语言可在各种计算机辅助设计工具中移植,而原理图输入工具是供应商独有的,不同供应商的原理图输入工具不同,因此原理图不能移植。除了这些标准语言,一些大的公司有他们自己的内部语言,一般在标准语言之前就已经开发出来,对他们自己的产品有一些独特的功能。无论哪种硬件描述语言,都用硬件描述语言编写的程序作为仿真器的输入。程序执行的步骤是分析、优化、初始化,最后仿真。分析与优化由编译器完成,这个编译器与其他程序设计语言的编译器类似。分析(analysis)检查是否存在与语法与语义规则相违背的描述,并产生设计的中间表示。优化(elaboration)遍历描述的各个设计层次,并将层次设计平铺成采用行为描述的模块的互联。分析与优化的最终结果是原始硬件描述语言设计的一个仿真模型,随后这个模型提交给仿真器执行。初始化(initialization)过程是设置仿真模型中所有变量为指定值或默认值。仿真器根据用户指定的一批输入或用户采用交互模式给定的输入来执行模块仿真。由于采用硬件描述语言可以有效地描述相当复杂的硬件,因此我们需要一种特殊的硬件描述语言结构,称为测试程序(testbench)。这个测试程序中包含了被测试的设计,通常称为被测设备(Device Under Test,DUT)。测试程序描述了硬件和软件的功能,给DUT提供输入,并验证产生的输出的正确性。这种方法避开了向仿真器分别提供输入并手工分析仿真输出的麻烦。测试程序提供了一个统一的验证结构,可以在自顶向下的设计过程中用来验证不同设计层次的正确性。逻辑综合正如前面所指出的那样,逻辑综合工具的有效性是硬件描述语言日益被广泛使用的驱动力之一。逻辑综合将一个电路RTL级的描述转换为一个优化后的网表,该网表包含了存储元件以及组合逻辑。随后利用物理设计工具可将网表转换为实际的集成电路版图。这个版图是集成电路制造的基础。逻辑综合工具处理设计中的大部分细节,并允许兼顾成本/性能间的平衡以提升设计的性价比。

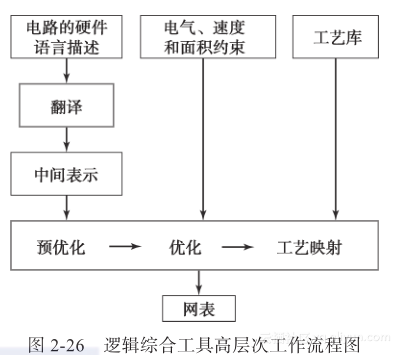

图2-26为逻辑综合步骤中一个简单的高层次工作流程图。用户提供待设计电路的硬件语言描述以及各种约束或者边界条件。电气约束包括允许的门扇出和输出负载限制。面积与速度约束指导综合中的优化过程。面积约束通常给出一个允许的最大面积,以保证一个电路能集成在集成电路中。

或者给出一个一般性的面积最小化的提示。速度约束给出电路中不同通道中允许的最大时延,或者给出一个一般性的使速度最快的提示。面积和速度约束与电路的成本直接相关。一个快速电路往往有较大的面积,因而制造成本也相应增加。如果电路速度不要求很快,则可优化其面积,相对而言,其生产成本降低。在一些顶级的综合工具中,功耗也可成为一个约束。综合工具的附加信息是工艺库(technology library),工艺库描述了网表中可用的原语块以及用于延迟计算所需的物理参数。后者是满足约束、执行优化必不可少的。在图2-26中,综合过程的第一个主要步骤是将硬件语言描述转换成一个中间形式。转换的结果可能是一些通用门与存储器件的相互连接,这些门和存储器不是直接从工艺库中得到的。转换结果也可能是另外一种形式。它包括一组一组的逻辑以及组与组之间的互联。综合过程的第二个主要步骤是优化。首先执行预优化以简化中间描述形式,例如在中间形式中,相同的逻辑用共享方式实现。然后就是优化,优化对中间形式进行处理以满足指定的约束。一般会执行两级和多级优化。优化后是工艺映射(technology mapping),工艺映射采用工艺库中的门代替原来的与门、或门和反相器。为了评估与这些门相关的面积与速度参数,需使用工艺库中的附加信息。在一些顶级的综合工具中,在工艺映射时会进行进一步的优化,以期能满足设计的约束条件。对于大电路来说,优化是一个非常复杂且耗时的过程。为了达到期望的结果或证明约束是困难的,可能要进行多次优化,当约束不能满足,如果可能,应该对其进行解释或论证。设计者可能需要修改约束或者修改程序来获得一个满意的设计,这些修改可能包括手工修改部分逻辑以达到设计目标。优化与工艺映射过程的输出是一个与原理图相对应的网表,该网表由存储单元、门和其他一些组合逻辑功能模块组成。这个输出可作为物理设计工具的输入,物理设计工具放置逻辑器件并确定它们之间的连线,以产生用于制造的电路版图。就可编程逻辑部件来说,例如对于第5章讨论的现场可编程逻辑门阵列,物理设计工具通过模拟产生二进制信息,这些二进制信息可以用来对可编程器件的逻辑功能进行编程。转载地址:http://ibhcx.baihongyu.com/

你可能感兴趣的文章

【Touch&input 】支持多个游戏控制器(18)

查看>>

我的友情链接

查看>>

SQL语句学习

查看>>

What is Cluster Aware Updating in Windows Server 2012?

查看>>

进老男孩的自我介绍和决心书

查看>>

线上Linux服务器运维安全策略经验分享

查看>>

Android一些问题的解决方案

查看>>

ios之UIToolBar

查看>>

centos 6.5 docker 安装

查看>>

C++静态局部对象

查看>>

一步步学习EF Core(3.EF Core2.0路线图)

查看>>

网络ASI

查看>>

Luogu P4707 重返现世

查看>>

目标与绩效管理实战专家胡立

查看>>

axios 中断请求

查看>>

2014手机分析图

查看>>

Linux PID 1 和 Systemd

查看>>

一元多项式相加

查看>>

commandLink/commandButton/ajax backing bean action/listener method not invoked (转)

查看>>

软件工作的大环境

查看>>